5.5.2.3.6.1.1. Алгоритм

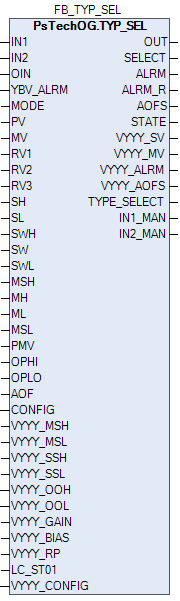

Функциональный блок TYP_SEL выполнен на основе базового функционального блока AS_HML, и, соответственно, наследует его функции. В таблице ниже представлен список основных функций блока.

|

Функция

|

Описание

|

|

Обработка тревог блока и формирование списка сработавших тревог (ALRM_R) и состояния тревог (ALRM).

| |

|

Маскирование тревог, т.е. тревоги формируются, но не записываются в журнал событий.

|

Функциональный блок TYP_SEL сравнивает сигналы от 2 блоков контроллера и автоматически выбирает минимальный/маскимальный сигнал в качестве управляющей выходной величины (MV). Другими словами, конечные элементы одного контура могут управляться таким образом, что с помощью блока селектора сигналов контролируются 2 переменные и поддерживаются на безопасной стороне заданных точечных значений, тогда как в обычном случае конечные элементы управляются на основе одной переменной.

Список доступных режимов функционального блока AS_HML:

Оператор не имеет возможности изменить положение селектора или установить значение вручную, всегда будет выбираться минимальное/максимальное значение.

Инициализация

По умолчанию блок инициализируется в режиме AUT.

Функция сигнализации

В случае обрыва (IOP) или состояния данных BAD одного из входов блок автоматически формирует сигнал тревоги IOP. В случае тревоги IOP одного из входов происходит автоматический переход на другой исправный вход.

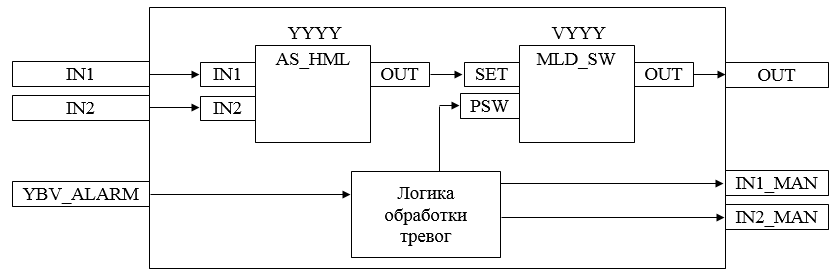

Функциональная блок-схема

На рисунке ниже показана функциональная блок-схема блока TYP_SEL:

Состав элементов блока TYP_SEL:

Блок YYYY базового типа AS_HML используется в качестве селектора сигналов с выбором максимального/среднего/минимального значения в зависимости от конфигурационного параметра CONFIG.TYPE_SELECT.

Подпрограмма логики обработки тревог используется для формирования воздействия на блоки YYYY и VYYY при изменении состояния тревоги входа.

В таблице ниже перечислены методы доступа к входам/выходам и адресаты соединения входов/выходов блока TYP_SEL:

|

Вход/Выход

|

Метод доступа

к входам/выходам

|

Адресат соединения

| |||

|

Каналы модулей

ввода/вывода ПЛК

|

Переменные

внешней логики

|

Входы/выходы функциональных блоков

| |||

|

IN1

|

Входной сигнал 1

|

Запись

|

-

|

x

|

x

|

|

IN2

|

Входной сигнал 2

|

Запись

|

-

|

x

|

x

|

|

OUT

|

Выход

|

Чтение

|

x

|

x

| |

x: соединение разрешено

-: соединение запрещено