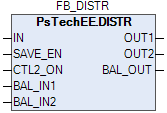

5.3.3.1.5. DISTR | РАСПРЕДЕЛИТЕЛЬ

Алгоритм позволяет:

передавать сигнал управления на один из двух выходов, например, когда один регулятор управляет двумя клапанами;

сохранять на отключенном выходе последнего (на момент отключения) значения сигнала управления;

выполнять каскадную балансировку источника сигнала управления.

Балансировка

В алгоритме реализована каскадная балансировка источника сигнала. Команда балансировки BAL_OUT повторяет команду на входе BAL_IN1, если CTL2_ON = FALSE, либо на входе BAL_IN2, если CTL2_ON = TRUE.

Если выбран режим памяти SAVE_EN = TRUE, то при изменении значения CTL2_ON алгоритм запоминает последние значения выходных сигналов OUT1 и OUT2 и записывает их в переменные OUT1_SAVE и OUT2_SAVE соответственно. При режиме памяти SAVE_EN = FALSE переменные OUT1_SAVE и OUT2_SAVE обнуляются.

Если вход CTL2_ON = FALSE значение выходного сигнала OUT1 равно входному сигналу IN. Значение выходного сигнала OUT2 либо обнулено, если режим памяти SAVE_EN = FALSE, либо равно сохраненному значению OUT2_SAVE, если режим памяти SAVE_EN = TRUE.

Если вход CTL2_ON = TRUE значение выходного сигнала OUT2 равно входному сигналу IN. Значение выходного сигнала OUT1 либо обнулено, если режим памяти SAVE_EN = FALSE, либо равно сохраненному значению OUT1_SAVE, если режим памяти SAVE_EN = TRUE.

Таблица состояний

Выходные сигналы формируются в соответствии с таблицей состояний.

|

CTL2_ON

|

SAVE_EN

|

BAL_OUT

|

OUT1

|

OUT2

|

|

FALSE

|

FALSE

|

BAL_IN1

|

IN

|

0

|

|

TRUE

|

FALSE

|

BAL_IN2

|

0

|

IN

|

|

FALSE

|

TRUE

|

BAL_IN1

|

IN

|

OUT2_SAVE

|

|

TRUE

|

TRUE

|

BAL_IN2

|

OUT1_SAVE

|

IN

|