5.5.2.4.7.4.1. Алгоритм

Технологический функциональный блок PID_SPR выполнен на основе базового функционального блока M_PID и, соответственно, наследует его функции.

|

Функция

|

Описание

|

|

Обработка измерительного входа и формирование переменной процесса (PV).

| |

|

Значение PV не формируется по значению измерительного входа (IN), а задается оператором вручную. Реальное значение измерительного входа (IN) отслеживается по значению параметра необработанных данных (RAW).

| |

|

Реализация алгоритма ПИД управления.

| |

|

Функция ограничения сброса выполняет коррекцию расчета ПИД-управляющих воздействий, используя значение, считанное с адресатов соединений через клеммы RL1 и RL2.

| |

|

Формирование выхода OUT в зависимости от значения управляющего выхода (MV).

| |

|

Обработка тревог блока и формирование списка сработавших тревог (ALRM_R) и состояния тревог (ALRM).

| |

|

Маскирование тревог, т.е. тревоги формируются, но не записываются в журнал событий.

| |

|

Проверка правильности задания уставок (HH, PH, PL, LL) для обработки тревог блока.

| |

|

Принудительный запрет формирования некоторых тревог по ремонтируемому оборудованию.

| |

|

Предотвращает резкое изменение управляющего воздействия MV при переходе режима с ручного MAN на автоматический AUT путем приравнивания значения задания SV к переменной процесса PV.

|

В данном разделе описывается программная функция для стандартного программного модуля ПИД-регулятора с выбором диапазона для систем АСУТП. Данный программный модуль будет использоваться для сбора результатов измерений и выполнять функцию непрерывного контроля через ПИД-алгоритм. Этот программный модуль может быть связан с другими типовыми элементами, такими как:

AI (аналоговый индикатор)

GCF (расход с компенсацией по температуре и давлению)

GCF_SQ (расход с компенсацией по температуре и давлению — извлечение квадратного корня)

Список доступных режимов:

Список доступных тревог:

Нормальное состояние (NR)

Высокая сигнализация размыкания входа (IOP)

Низкая сигнализация размыкания входа (IOP-)

Сигнализация достижения 2-го верхнего предела (HH)

Сигнализация достижения 2-го нижнего предела (LL)

Сигнализация достижения верхнего предела (HI)

Сигнализация достижения нижнего предела (LO)

Сигнализация по верхнему отклонению + (DV+)

Сигнализация по нижнему отклонению - (DV-)

Скоростная сигнализация + (VEL+)

Скоростная сигнализация - (VEL-)

Сигнализация избыточного значения выхода (MHI)

Сигнализация недостаточного значения выхода (MLO)

Сигнализация нарушения соединения (CNF)

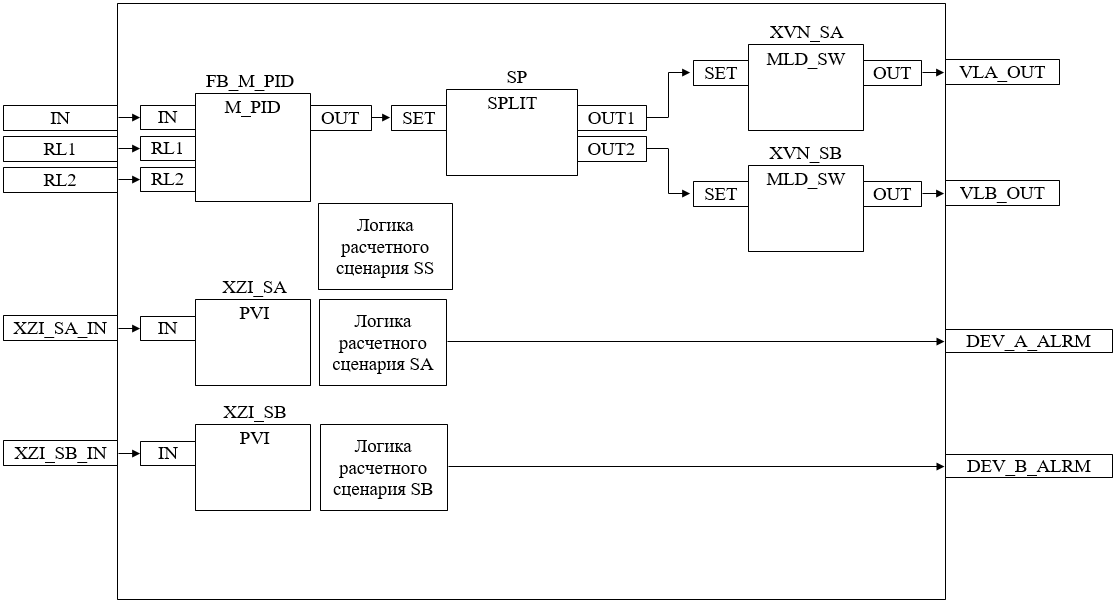

Функциональная блок-схема

Состав элементов блока:

Блок FB_M_PID базового типа M_PID обеспечивает функцию пропорционально-интегрально-дифференциального регулирования с учетом отклонения технологической переменной (PV) от значения уставки (SV).

Блок XZI_SA базового типа PVI используется для индикации значения позиционной обратной связи клапана A.

Блок XZI_SB базового типа PVI используется для индикации значения позиционной обратной связи клапана B.

Подпрограмма логики расчетного сценария SA используется для генерирования сигнала об отклонении клапана A.

Подпрограмма логики расчетного сценария SB используется для генерирования сигнала об отклонении клапана B.

Блок XVN_SA базового типа MLD_SW используется в качестве блока управления выходом задания положения для клапана A.

Блок XVN_SB базового типа MLD_SW используется в качестве блока управления выходом задания положения для клапана B.

Подпрограмма логики расчетного сценария SS используется для выполнения функции отслеживания.

Блок SP базового типа SPLIT используется для разделения диапазона между двумя клапанами, настройки рабочего диапазона и типа работы (прямой или обратный) клапанов.

Методы доступа к входам/выходам и адресаты блока:

|

Вход/Выход

|

Метод доступа

к входам/

выходам

|

Адресат соединения

| |||

|

Каналы модулей

ввода/

вывода ПЛК

|

Переменные

внешней

логики

|

Входы/выходы функциональных блоков

| |||

|

IN

|

Измерительный вход

|

Запись

|

x

|

x

| |

|

VLA_OUT

|

Выход управления клапаном A

|

Чтение

|

x

|

x

| |

|

VLB_OUT

|

Выход управления клапаном B

|

Чтение

|

x

|

x

| |

|

XZI_SA_IN

|

Вход обратной связи положения A

|

Запись

|

x

|

x

| |

|

XZI_SB_IN

|

Вход обратной связи положения B

|

Запись

|

x

|

x

| |

x: соединение разрешено

-: соединение запрещено

Основные функции

функция контроля с использованием ПИД-алгоритма

ошибка аналогового входа и выхода

функция регулирования с диапазоном выбора

запрет технического обслуживания измерения

останов технологического процесса (связанный с положением клапана и выключателем безопасности)

Подробное описание

Регулировка выхода:

Для закрытых при отказе клапанов FC, -- 0% для закрытия (4 мА) 100% для открытия (20 мА)

Для открытых при отказе клапанов FO, -- 0% для закрытия (20 мА) 100% для открытия (4 мА)

Подробное описание

Индивидуальное управление обоими клапанами: Независимо от режима работы блока ПИД-регулятора, т.е. АВТО (КАСКАД) / РУЧН, оператор может получить доступ к управлению каждым клапаном, используя блок управления выходом. Когда оба блока управления выходом работают в режиме КАСКАД (нормальные условия эксплуатации), оператор может изменить режим на РУЧН и изменить окончательное значение выхода.

Ручной режим: ПИД-алгоритм отключается, и оператор может задать окончательное значение выхода MV. Уставка SV отслеживает значение измерения PV. Отслеживание уставки можно отменить на основании функционального анализа.

Автоматический режим: В режиме АВТО нормальный ПИД-алгоритм выполняется с уставкой оператора SV.

Состояние ошибки аналогового выхода: Разомкнутый выход OOP будет активирован, когда контур разомкнут или в случае неисправности соответствующей платы.

Функция запрета технического обслуживания: Когда соответствующее измерение запрещено, ПИД-алгоритм отключается, а окончательное значение выхода фиксируется на последнем вычисленном окончательном значении выхода. Оператор не может изменить уставку SV, ПИД-регулятор и блоки выхода принудительно переключается в режим РУЧН, и оператор может изменить окончательное значение выхода MV.

Останов технологического процесса: Возможны два варианта:

В случае защитной блокировки выход ПИД-регулятора будет принудительно настроен на заданное состояние, и доступ оператора будет запрещен до отключения блокировки.

Для блокировки технологического процесса на выход ПИД-регулятора передается эталонное значение с помощью короткого импульса 2 с, при этом доступ оператора разрешен.

Примечание: Когда вход (программный модуль аналогового входа), связанный с ПИД-регулятором, находится в состоянии ошибки (IOP+ или IOP-), ПИД- регулятор принудительно переключается в режим РУЧН, а исполнение алгоритма управления отключается.

Для работы алгоритма выбора диапазона перевести внутренние блоки XVN_SA и XVN_SB в каскадный режим, задав на входы XVN_SA_MODE и XVN_SB_MODE значение CAS.